AMD recently submitted a patent with the World Intellectual Property Organisation (WIPO) that suggests the company wants to vastly improve the performance of the current DDR5 memory standard. It outlines what the company calls a “high bandwidth memory module architecture”, and should boost data rates for the memory standard to double what it is currently outputting.

AMD argues that the current state of DDR5 is unable to keep up with the growing memory bandwidth, particularly in operations and applications that require high-performance graphics processors and servers. As it stands, the current state of the architecture is already hitting performance ceilings, while every other performance metric relative to it, continues to improve.

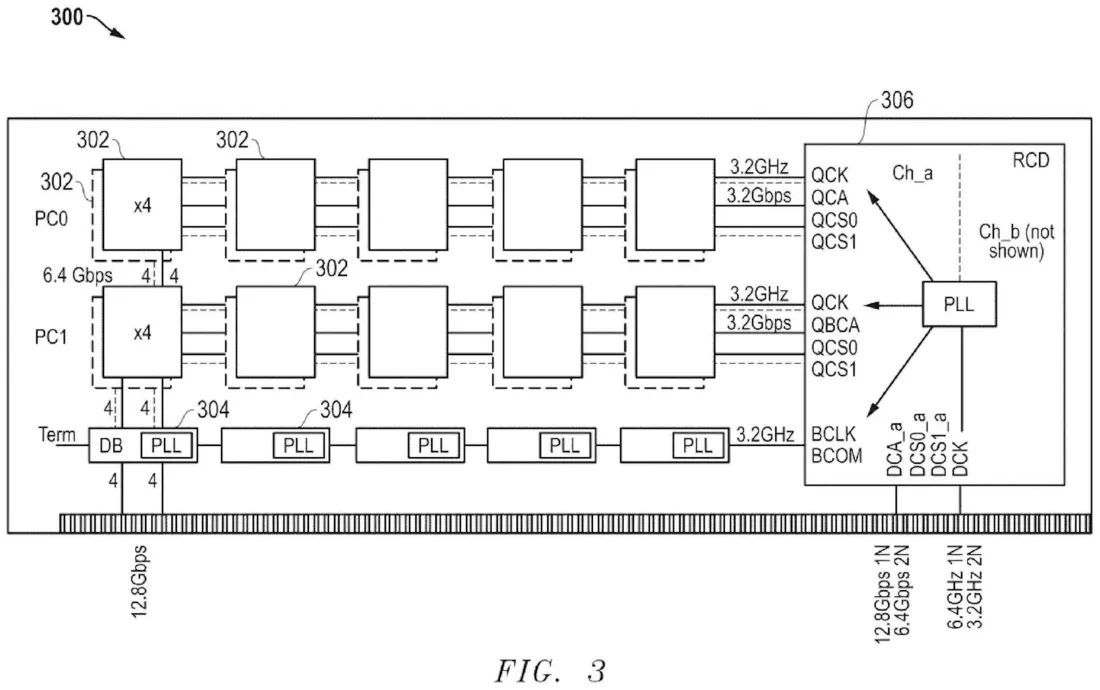

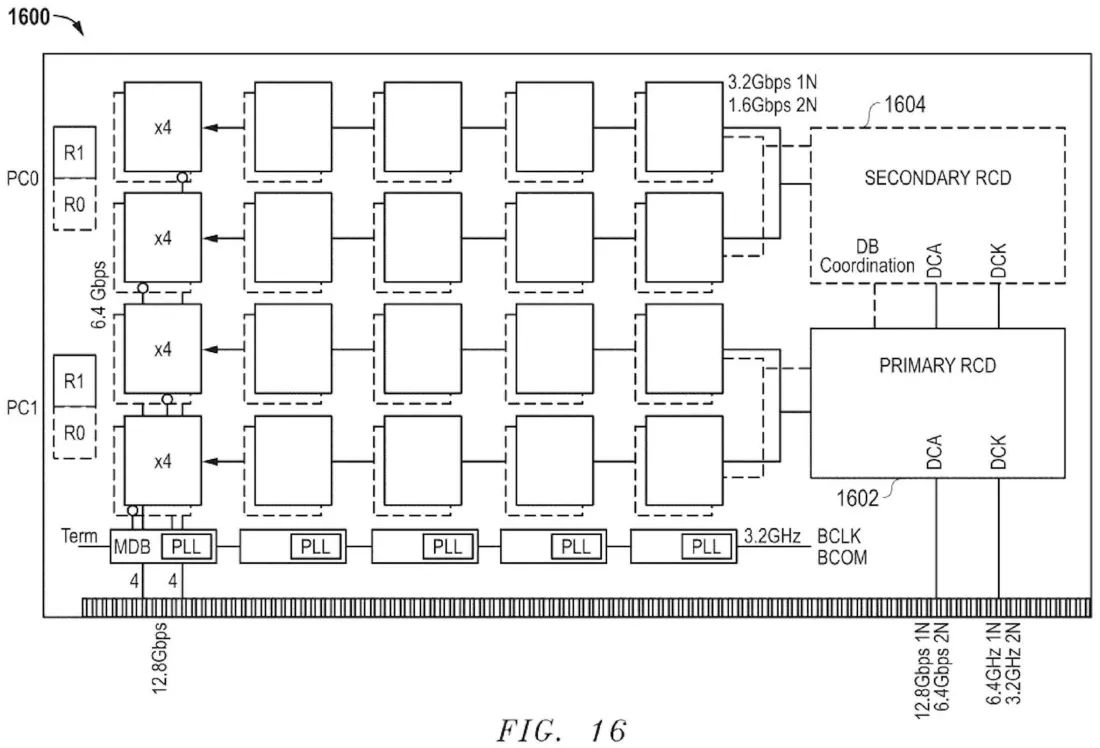

Specifically, the patent points to a data rate of 12.8 Gbps on the memory bus. That’s double the native 6.4 Gbps of the current DDR5 chips. With the new HB-DIMM architecture, it doesn’t necessarily change the underlying DRM chips, and even scales the performance with the existing technology.

Also at the core of this new DDR5 architecture is a register clock driver circuit that decodes memory commands and routes them using a chip identifier bit. In effect, this will allow the module to assign tasks between pseudo-channel and quad-rank configurations, making pretty versatile for systems in high-performance computing environments, where memory bandwidth is critical.

This isn’t the first time AMD has filed patents aimed at improving performance on currently existing hardware, and through meaningful, effective, and impactful engineering. Prior to this, the red chipmaker filed patents that included a blower fan design, aimed at improving the thermals inside gaming laptops, as well as a cache memory cleaning system that would help boost processor efficiency.

(Source: Tech4Gamers, Techspot)